Understanding of operating condition-based analysis is very important, if you really want to be expert in Static Timing Analysis. PVT (like Process, Voltage and Temperature) corners, Interconnect corners, Design Corners are all inter-related and these numbers are increases day by day. These are few topics where people have a lot of confusion (and there was time even I was at the same stage). Still sometime I become confused. But still, I am trying to capture my understanding here as per my experience & try to simplify these concepts as much as possible. In this series of Articles, I am going to discuss about this in very detail. I will try my best to cover as much as possible in a simple language.

Let’s start with the Type of Analysis based on Operating Conditions & then we will go one step down to understand concepts in great detail. I am sure all of you will Like this series of Articles.

Type of Analysis based on Operating Conditions

When we have studied (in college days) about the Semiconductor devices & different equations & respective parameter, we have noticed that these parameters have dependency on Environment Temperature or Fabrication Process or Voltages. There are few constants which we have used in the equations & if you will try to find out the concepts behind the value of those constants, you will see that there is certain assumption made and if you try to remove those assumption – equation become more complex. We are going to discuss all these in this series of Articles by like I said one by one.

In lot of books/manuals/readme/flow/methodology/articles, you will see people usually talk about 3 type of Analysis mode for STA (Static Timing Analysis) on the basis of Operating conditions. Those 3 analysis modes are…

Single Operating condition Analysis mode - means it’s going to use single set of Delay values for whole circuit based on Process, Voltage and Temperature. For example, reading only 1 .lib file for setup and Hold analysis.

BC_WC Operating condition Analysis mode – it’s known as Best case Worst Case operating mode. It means we are going to use 2 extreme set of delay values simultaneously based on respective Process, Temperature & Voltage. For example, you are going to use 2 .lib files for Setup and Hold Analysis. For Setup check, we use Max & Min delay values from 1 .lib file and for Hold Check - Max & Min delay values from another .lib file.

OCV Operating condition Analysis mode – OCV stands to On-Chip-Variation. We will discuss this in detail later. In this mode, we use 2 set of delay values at the same time for Timing Analysis. For example – For Setup analysis, Max delay for Launch Clock path & Data path; Min delay for Capture clock path from both set of Libraries. Similarly – For Hold Analysis, Min delay for Launch Clock path & Data path; Max delay for Capture Clock path.

Note: Please read the difference between BC_WC Vs OCV mode.

I am sure, you become more confuse. No problem 😊 … Let’s take an example and try to understand this.

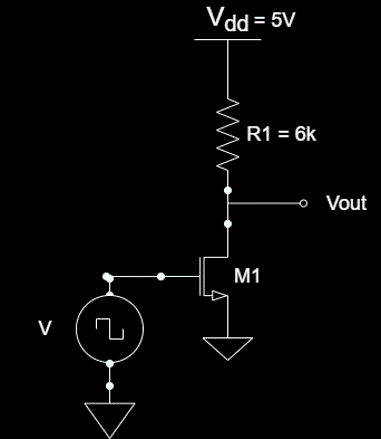

We have a small circuit as per below Fig; 2 set of Libraries (.lib files) example_bc.lib & example_wc.lib. For easy understanding I am using delay values directly (detailed calculation of delay value will discuss in next Article).

Combination Logic Delay as per example_bc.lib

For Falling waveform at Q1: 7ns

For Rising waveform at Q1: 5ns

|

Buffer delay as per example_bc.lib

Fall delay = 2ns

Rise delay = 3ns

|

Clock2Q delay as per example_bc.lib

0.8ns if falling waveform at Q1

1.0ns of rising waveform at Q1

|

Combination Logic Delay as per example_wc.lib

For Falling waveform at Q1: 10ns

For Rising waveform at Q1: 8ns

|

Buffer delay as per example_wc.lib

Fall delay = 3ns

Rise delay = 4ns

|

Clock2Q delay as per example_bc.lib

1.0ns if falling waveform at Q1

1.2ns of rising waveform at Q1

|

Setup Time of FF2 = 2.5ns

Hold Time of FF2 = 3ns

Clock Time Period = 10ns

Few other assumptions during the analysis:-

Note:

- I have just mentioned the delay values directly as per the circuit but actually tool is going to calculate the delay value based on Transition time and output Load. To understand that part please refer my other articles.

- Setup and Hold Time also have dependency on type of waveform at D2 pin but right now just making it simple. 😊

Let’s try to understand how the calculation happen in all 3 Mode for Setup and hold Analysis. But before that I want you to revise the Setup and Hold Slack equation. 😊 You can also check my other article for this http://www.vlsi-expert.com/p/static-timing-analysis.html

Setup Slack = Required Time – Arrival Time

Required Time (RT)= Capture Clock Path delay (Min) + Time Period – Setup Time

Arrival Time (AT)= Launch Clock path Delay (Max) + Clock2Q Delay (max) + Datapath delay (Max)

Hold Slack = Arrival Time - Required Time

Required Time (RT) = Capture Clock Path delay (Max) + Hold Time

Arrival Time (AT) = Launch Clock path Delay (Min) + Clock2Q Delay (Min) + Datapath delay (Min)

Single Operating Mode:

As we have discussed, for such analysis we provide only one delay table for Setup ad Hold analysis. In our case we have 2 .lib files that means we can do 2 analysis.

Single Operating condition analysis using example_bc.lib

Setup Analysis:

RT = 3 x (Buffer Rise Delay) + 10ns – (Setup Time) = 3x3ns + 10ns -2.5ns = 16.5ns

AT = 3 x (Buffer Rise Delay) + Clock2Q Delay (falling waveform at Q1) + Combinational Delay (Falling waveform at Q1)

= 3x3ns + 0.8ns + 7ns = 16.8ns

Setup Slack = RT – AT = 16.5ns – 16.8ns = -0.3ns (Violation)

Question

- I have picked Rise Buffer delay in both cases, Why?

- I have used Clock2Q delay is for falling waveform at Q1 even though Rising waveform Delay at Q1 is more then falling waveform delay at Q1, Why?

Hold Analysis:

RT = 3 x (Buffer Rise Delay) + (Hold Time) = 3x3ns + 3ns = 12ns

AT = 3 x (Buffer Rise Delay) + Clock2Q Delay (Rising waveform at Q1) + Combinational Delay (Rising waveform at Q1)

= 3x3ns + 1.0ns + 5ns = 15ns

Hold Slack = AT – RT = 15ns – 12ns = 3ns (No Violation)

Single Operating condition analysis using example_wc.lib

Setup Analysis:

RT = 3 x (Buffer Rise Delay) + 10ns – (Setup time) = 3x4ns + 10ns -2.5ns = 19.5ns

AT = 3 x (Buffer Rise Delay) + Clock2Q Delay (falling waveform at Q1) + Combinational Delay (Falling waveform at Q1)

= 3x4ns + 1.0ns + 10ns = 23ns

Setup Slack = RT – AT = 19.5ns – 23ns = -3.5ns (Violation)

Hold Analysis:

RT = 3 x (Buffer Rise Delay) + (Hold time) = 3x4ns + 3ns = 15ns

AT = 3 x (Buffer Rise Delay) + Clock2Q Delay (Rising waveform at Q1) + Combinational Delay (Rising waveform at Q1)

= 3x4ns + 1.2ns + 8ns = 21.2ns

Hold Slack = AT – RT = 21.2ns – 15ns = 6.2ns (No Violation)

Single Mode Analysis Summary

| Analysis Type | Using Library example_bc.lib | Using Library example_wc.lib |

| Setup Slack | -0.3ns | -3.5ns |

|---|

| Hold Slack | 3ns | 6.2ns |

|---|

So, in this mode you have to do 2 separate analysis. Tool will read only 1 .lib at a time and perform analysis as per that.

There may be couple of questions in your mind in terms of values while doing setup and hold analysis. I say either wait for some time or revise your concepts once again. 😊

Let’s Jump to the second Mode of analysis

Min_Max (Bc_Wc) Operating Mode:

In this mode we have to provide or say define 2 set of libraries inside the tool – one as Best-case Library and other as worst-case library. Like we already have 2 libraries – so just define it.

Best_Case_Library = example_bc.lib

Worst_case_Libary = example_wc.lib

You can ask me on what basis we are going to define it – means in our case, library name itself has bc/wc, so is it the criteria? What if library name doesn’t have such nomenclature? Simple Answer from my side it – you have to get an IDEA for this. If you define these libraries randomly, your analysis is not going to be a good analysis. Generally, in most of the companies there is a separate Team which do all these experiments and update you which is Best/worst library, so you can use that as your reference OR if you want to know yourself – This series of Articles is for you. 😊 We are going to discuss all these in detail in coming articles. But for now, just use above case and try to understand how it will impact the analysis.

Setup Analysis:

For Setup, we (or say tool) are going to use only worst-case library defined by you i.e. example_wc.lib

RT = 3 x (Buffer Rise Delay) + 10ns – (Setup time) = 3x4ns + 10ns -2.5ns = 19.5ns

AT = 3 x (Buffer Rise Delay) + Clock2Q Delay (falling waveform at Q1) + Combinational Delay (Falling waveform at Q1)

= 3x4ns + 1.0ns + 10ns = 23ns

Setup Slack = RT – AT = 19.5ns – 23ns = -3.5ns (Violation)

Hold Analysis:

For Hold, we (or say tool) are going to use only best-case library defined by you i.e. example_bc.lib

RT = 3 x (Buffer Rise Delay) + (Hold Time) = 3x3ns + 3ns = 12ns

AT = 3 x (Buffer Rise Delay) + Clock2Q Delay (Rising waveform at Q1) + Combinational Delay (Rising waveform at Q1)

= 3x3ns + 1.0ns + 5ns = 15ns

Hold Slack = AT – RT = 15ns – 12ns = 3ns (No Violation)

BC_WC Mode Analysis Summary:

| Analysis Type | Best Case Library = example_bc.lib

Worst Case Library = example_wc.lib |

|---|

| Setup Slack | -3.5ns |

|---|

| Hold Slack | 3ns |

|---|

If you will compare BC/WC operating mode analysis with Single Mode Analysis, you may realize that both are same as such only difference is – we are doing less no. of analysis in BC/WC mode. Yes, you are right and don’t think we are losing anything. For Setup, we want to make sure that even in worst case – my design should work – so for that we are doing worst case analysis, For Hold, we want to make sure that even in Best case scenario my design should work and that’s the reason we did best case analysis. As such, rest 2 analysis are not required. So, we are saving a lot of Run Time also. Saving a lot of Tool runtime + Memory + CPU uses + Human analysis time. That’s the importance of BC_WC_Operating_mode Analysis.

Now, Let’s try to understand the 3rd Mode of Analysis.

On-Chip-Variation Analysis Mode:

There are lot of concepts in this mode but we are going to discuss only basic one right now. Later in series, we will extend this mode and discuss in detail. So, as we have discussed that in this mode also we are going to use 2 set of libraries and we have to define the worst and best case libraries as we have done in case of BC_WC_Operating Mode but difference is in the way we are performing Setup and Hold analysis.

If you will see the Setup and Hold Slack equations – (Again pasting here)

Setup Slack = Required Time – Arrival Time

Required Time (RT)= Capture Clock Path delay (Min) + Time Period – Setup Time

Arrival Time (AT)= Launch Clock path Delay (Max) + Clock2Q Delay (max) + Datapath delay (Max)

Hold Slack = Arrival Time - Required Time

Required Time (RT) = Capture Clock Path delay (Max) + Hold Time

Arrival Time (AT) = Launch Clock path Delay (Min) + Clock2Q Delay (Min) + Datapath delay (Min)

We have talked about the min delay for capture clock path and max delay in launch clock path in case of setup but in above 2 analysis mode (Single Mode analysis & BC_WC_mode), we are not using different set of delays for different paths. Yes, you got the point correctly – in this mode we will do analysis keeping this in considering.

Best_Case_Library = example_bc.lib

Worst_case_Libary = example_wc.lib

Setup Analysis:

For Setup, we (or say tool) are going to use worst-case means max delay for Arrival path (Arrival Time) from the library defined as worst_case library (i.e. example_wc.lib ) and best-case means min delay for Required Path (Required Time) from the library defined as best_case library (i.e. example_bc.lib )

RT = 3 x (Buffer Rise Delay from Library example_bc.lib) + 10ns – (Setup time)

= 3x3ns + 10ns -2.5ns = 16.5ns

AT = 3 x (Buffer Rise Delay from Library example_wc.lib) + Clock2Q Delay (falling waveform at Q1, as per library example_wc.lib) + Combinational Delay (Falling waveform at Q1, as per library example_wc.lib)

= 3x4ns + 1.0ns + 10ns = 23ns

Setup Slack = RT – AT = 16.5ns – 23ns = -6.5ns (Violation)

Hold Analysis:

For Hold, we (or say tool) are going to use bst-case means min delay for Arrival path (Arrival Time) from the library defined as best_case library (i.e. example_bc.lib ) and worst-case means max delay for Required Path (Required Time) from the library defined as worst_case library (i.e. example_wc.lib )

RT = 3 x (Buffer Rise Delay from Library example_wc.lib) + (Hold Time) = 3x4ns + 3ns = 15ns

AT = 3 x (Buffer Rise Delay from Library example_bc.lib) + Clock2Q Delay (Rising waveform at Q1, as per Library example_bc.lib) + Combinational Delay (Rising waveform at Q1, as per Library example_bc.lib)

= 3x3ns + 1.0ns + 5ns = 15ns

Hold Slack = AT – RT = 15ns – 15ns = 0ns (No Violation)

OCV Mode Analysis Summary:

| Analysis Type | Best Case Library = example_bc.lib

Worst Case Library = example_wc.lib |

| Setup Slack | -6.5ns |

|---|

| Hold Slack | 0ns |

|---|

Now, lets compare all the 3 mode and see what’s our finding and I am sure you can yourself decide the advantage of each mode.

Remember:

Best_Case_Library = example_bc.lib

Worst_case_Libary = example_wc.lib

| Analysis Type | Single Mode | BC_WC Mode | OCV Mode |

|---|

| BC Library | WC library |

| Setup Slack | -0.3ns | -3.5ns | -3.5ns | -6.5ns |

|---|

| Hold Slack | 3ns | 6.2ns | 3ns | 0ns |

|---|

Note:

- OCV mode is more closure toward the real scenario –

- If you fix setup slack in this mode – it will fix in other mode of analysis also.

- If there is no Hold Violation in this mode – it will not be in other 2 also

Still, Lot of questions are there related to these 3 modes, Wait for next Article in next week.