Background of Types of Dielectric layer

Dielectric layers are of 2 types.

- Planar Dielectric

- Conformal Dielectric

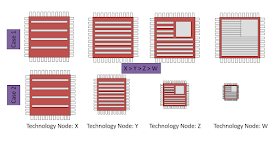

Below figures can help you to refresh your memories about Planar and Conformal dielectric.

Planar Dielectric:

All Dielectric in the below figure (D1 to D7) are Planar dielectric.

Conformal Dielectric:

Different type of Conformal dielectric structures are shown in below figure. There are certain parameters which helps to identify any conformal dielectric like Side thickness, Bottom thickness or Top thickness.

Modelling of Dielectric in Technology File

Modelling of Dielectric layer in technology file vary as per extraction software or you can say that as per EDA vendor. Different EDA vendor uses different ways to represents this as per their requirement. Even if I know their syntax, I can't write here. :) But what I am going to do - explain everything in more easy language. :) Once you start working, you can check their manual and try to map my syntax with their syntax. :)

To represent a Planar Dielectric (Non-Conformal) we need to have following basic information.

(Parameter Name : my_nomenclature )

Dielectric constant : di_constant

Thickness : thickness

Height from the Substrate : height

Name of Dielectric : DIELECTRIC

Type of Dielectric : conformal=false

To represent a Conformal Dielectric we need to have following extra information.

(Parameter Name : my_nomenclature )

Side Thickness : S_thickness

Bottom Thickness : B_thickness

Top Thickness : T_thickness

Type of Dielectric : conformal=true

Parent Layer : p_layer (This is the layer around which dielectric is present. It can be a conductor like Poly, Metal1 or may be any other Dielectric also. In above figure, M1 is the Parent layer).

Planar Dielectric

Modelling in Technology file:

DIELECTRIC DEL2

di_constant = 4.8

thickness = 2.7

height = 4.1

conformal = false

DIELECTRIC DEL3

di_constant = 2.8

thickness = 0.3

height = 6.8

conformal = false

Conformal Dielectric

There are different scenarios which need to understand. These scenarios are same as we have discussed in the article of Conformal Dielectric (It will help you to map easily)

Scenario 1:

Modelling in Technology file:

DIELECTRIC DEL_M1a

conformal = true

T_thickness = 0.2

S_thickness = 0.2

B_thickness = 0

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

DIELECTRIC DEL_M1b

conformal = true

T_thickness = 0

S_thickness = 0.2

B_thickness = 0.2

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

Scenario 2:

Modelling in Technology file:

DIELECTRIC DEL_a

conformal = true

T_thickness = 0.2

S_thickness = 0

B_thickness = 0

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

DIELECTRIC DEL_b

conformal = true

T_thickness = 0

S_thickness = 0.2

B_thickness = 0

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

DIELECTRIC DEL_c

conformal = true

T_thickness = 0

S_thickness = 0

B_thickness = 0.2

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

Scenario 3:

Representation of DEL_a1, DEL_a2 and DEL_a3 in Technology file:

DIELECTRIC DEL_a1

conformal = true

T_thickness = 0.2

S_thickness = 0

B_thickness = 0

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

DIELECTRIC DEL_a2

conformal = true

T_thickness = 0.15

S_thickness = 0

B_thickness = 0

di_constant = 2.8

thickness = 0

height = 4.1

p_layer = DEL_a1

DIELECTRIC DEL_a3

conformal = true

T_thickness = 0.15

S_thickness = 0

B_thickness = 0

di_constant = 1.8

thickness = 0

height = 4.1

p_layer = DEL_a2

Remember: In above representation, for DEL_a2, p_layer is previous dielectric (i.e DEL_a1). It's because this dielectric has parent layer DEL_a1. It's deposited on the top of DEL_a1. Top thickness also measured with respect to DEL_a1.

Note: you might be thinking why Height parameter is same in all 3 cases. It depends on EDA vendor, how they want to represent the height of Conformal layer. Here I am assuming that my tool is going to automatically measure actual height with the help of provided data. :)

Representation of DEL_b1 and DEL_b2 in Technology file:

DIELECTRIC DEL_b1

conformal = true

T_thickness = 0

S_thickness = 0.2

B_thickness = 0

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

DIELECTRIC DEL_b2

conformal = true

T_thickness = 0

S_thickness = 0.15

B_thickness = 0

di_constant = 2.8

thickness = 0

height = 4.1

p_layer = DEL_b1

Similarly, Representation of DEL_c1 and DEL_c2 in Technology file:

DIELECTRIC DEL_c1

conformal = true

T_thickness = 0

S_thickness = 0

B_thickness = 0.2

di_constant = 3.8

thickness = 0

height = 4.1

p_layer = M1

DIELECTRIC DEL_c2

conformal = true

T_thickness = 0

S_thickness = 0

B_thickness = 0.15

di_constant = 2.8

thickness = 0

height = 4.1

p_layer = DEL_c1

Scenario 4:

Modelling in Technology file:

DIELECTRIC DEL2

conformal = true

T_thickness = 0.1

S_thickness = 0.2

B_thickness = 0.0

di_constant = 2.8

thickness = 0.4

height = 4.1

p_layer = M1

DEL2 is a conformal dielectric & the reason behind this is - It has a Side Thickness and Top thickness parameter. But you may be thinking that it looks like a planar at all other places, it's shape is similar to non-conformal dielectric. I can understand your confusion. Actually, you are right that at certain places it's conformal and at some places it's non-conformal.

In the representation of all conformal layer, you may have noticed that thickness parameter is 0. It's because they dnt have any thickness as such (I am not talking about top thickness. That's a different parameter). In this case, this thickness parameter is non-zero like in case of Planar dielectric.

At the end, I just wanted to highlight once again that different EDA vendors have different syntax and different way to represent dielectric layers in technology file. Above representation is just for your understanding purpose, it's not specific to any company.