Create N-well And Field Oxide

If you think, I can explain the complete manufacturing steps in a single post then it’s not possible. So I will discuss this in a series of 4-5 post. Best part is – I will try to explain more with pictures and explain them in very short (in text). I will only discuss the concepts in between (if required). I have tried to make figures/diagram self explanatory. But still in case of confusion, feel free to ask me.

Complete CMOS fabrication, I have divided into different post based on below milestones.

We want to fabricate a CMOS Inverter.

In the above diagram – you may have few questions and doubts. Let me add few points here which can help you.

Only Photoresist is not sufficient to shield Silicon from Ion Implantation. So Oxide or Nitride is required to block the implant.

There are 2 portion of Photoresist. Soluble/Soft portion (Portion on which UV rays falls) and Hard portion (Which is not exposed by UV)

Solvent required to remove/dissolve the soft portion of photoresist is different from the solvent required to remove the hard portion.

For CMOS process, both NMOS (N- Channel transistor) and PMOS (P-Channel transistor) are required.

We always talk about the P-type substrate and Not N-type Substrate. Question is why?

It’s not like P-Type substrate is available in the market and we are just using that. In the Market Silicon wafer is available and with the help of Doping – we convert that silicon wafer into P-type substrate. Now you will ask why we can’t convert this into N-type Substrate. And I will simple say – you can do that. No one is going to stop you. They why it’s not well known?

Actually – we can’t use 2 different substrate for design because in the design both PMOS and NMOS is present. We have to choose which is more beneficial from fabrication point of view. In general or say it’s true that NMOS devices are always more in the Semiconductor Industry in comparison to PMOS devices. For your reference-SRAM requires 6 transistors (4 NMOS, 2 PMOS)

Another reason for more number of NMOS is because of difference of mobility of electron and Holes. Electron mobility is almost twice of holes mobility and because of this ON-RESISTANCE of n-channel device is half of p-channel device with the same geometry and under the same operating conditions. That means to achieve same impedance size of n-channel transistors is almost half of p-channel devices. Same thing I can say in the different way that for same size of wafer, we can have more number of NMOS (means can perform more logical operation) in comparison to PMOS.

I hope above explanation helps you to understand the reason of well-known P-type Substrate. :)

For NMOS – we doped entire silicon wafer first with P-type impurities and make it P-type Substrate, where we can directly form N-channel devices.

For PMOS – we have to separately create N Well selectively (by adding N-type Impurities in the selective regions).

Twin Tub (Twin-Well) CMOS Process:

There is a process where both type of Wells (N- Well and P Well) are present. Such process is known as Twin Tub (Twin-Well) CMOS process.

This process is required when we want to optimize different parameters independently (like threshold voltage, body effect and the channel transconductance). If we have p-type of substrate then all the NMOS can’t be optimized independently (because they have common P-type substrate). Similarly N-well is with in P-substrate, then there is some influence of this on PMOS also. I am not going to discuss all this right now. It’s just for your info.

Device Isolation/Field Oxide (Channel Stop implants)

As I have mentioned above for better performance Devices should be electrically isolated from each other (both same type and different type of devices). Basically we want to suppress leakage current.

Best solution is to form a reverse bias pn-junction between 2 transistors. That means if we form positive doped region next to the negatively doped region (N-well next to P-well or vice versa), they can automatically form a reverse bias between 2 regions. Till the point there is a depletion layer between them, except reverse saturation current (very small leakage current) there will be no electrical connection between these 2 regions until voltage exceed breakdown voltage. To control the voltage between these 2 regions, we can tie n-region to most positive voltage (VDD) and p-region to most negative voltage (VSS).

Junction leakage current has dependency on the area of the depletion layer, so in case of large n and p region, this current will be significant and it will not solve the complete purpose.

In such cases, there is another general method – forming the dielectric layer between 2 transistors. This dielectric is very thick and known as Field Region (Field Oxide).

Few points about the Field Oxide

Also known as Thick Oxide, Thick SiO2 insulator.

Field Oxide is Thickest Oxide relative to other oxide layer present in the IC (e.g. Gate Oxide layer)

This oxide region is different from the Gate oxide.

The area where Field Dielectric is not present, is the area where Transistor exist. And this area is known as active region.

There are 2 ways to form the Field Oxide Region (We will not discuss these 2 methods right now).

Field Oxide increases the transistor’s threshold voltage so that device always remains in Off-stage. This threshold voltage can be further increased by increasing the surface doping concentration, Called “Channel Stop” under the Field Oxide.

So the Isolation region are formed by 2 layers

To increase the threshold voltage as much as possible, Channel shop region should be highly doped and Field Oxide layer should be as thick as possible.

Size of above final figure is small for clarifying the further processing. So now I am just expanding that and start the process from there on.

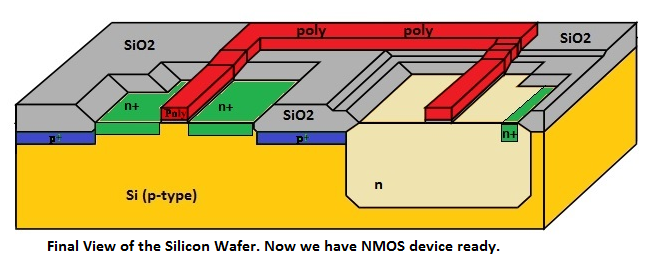

End results will be something similar to the below one (in 3D).

Till now we have created

- Nwell

- Active Region

- Channel Stop Region

- Field Oxide.

In the next post we will talk about Gate Oxide.