CMOS Layout Design: Introduction

| Index | Chapter1 | Chapter2 | Chapter3 | Chapter4 | Chapter5 |

| Digital Background | Semiconductor Background | CMOS Processing | CMOS Basic | CMOS Layout Design |

| 5.1 | 5.2 |

| Layout Design Introduction | Design Rule Check (DRC) |

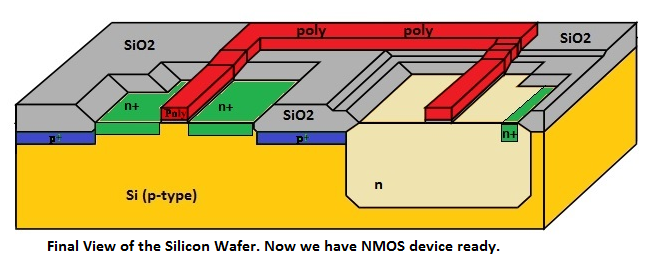

In the CMOS Processing series, we have learnt about the different fabrication steps in more detail with the help of diagrams. I have also mentioned that those were basically the side view of the fabrication process. I have also try to summarize each article with the help of 3D view. But in the world of CAD tools, designers talks about the TOP view, which is known as LAYOUT of the design. We will learn more about the layout in detail in the next few articles, but this article will help you to understand the CMOS layout based on fabrication steps which we have learn in the CMOS fabrication series.

In this article, I will summarize the TOP view along with the 3D and side view. I am sure it will help you to understand the layout of CMOS inverter.

Note: Before I will start the layout of CMOS, Just wanted to make one thing very clear that during the layout designing, sequence of different layers in a mask layout is completely arbitrary, it does not have to follow the actual fabrication sequence. Layout is drawing the masks used in the manufacturing process. So at the end of the day, Foundry is going to create different Mask on the basis of Layout which designer has prepared. So from Foundry side, it doesn’t matter in which sequence you have design the Layout/mask. For them it’s matter whether Mask is correct or not. How this Layout info transferred to Foundry and in which form – we will discuss all this later on.

I will use following layers during our discussion.

I am sure you have question about the N-select and P-select because we never discussed about these layers till now. What are there layers and what’s the use of these? Let me explain these first before we start anything.

Active and N/P Select layers:

Active layer in a layout defines openings in the silicon-di-oxide covering the substrate. N-select or P-select layers indicates where to implant n-type or P-type atoms respectively. The active and select layers are always used together.

Consider the below figure. Here we have took example of the Substrate as a BOX which has Field Oxide (FOX) on the top of that. You can see that the Active layer as a BOX which indicates where to open a hole in the field oxide. These openings are called Active Area. Rest of the Field area (which is not the active area) is used for the routing purpose.

MOSFETs are fabricated in these active areas or you can say these active openings (both PMOS and NMOS). Pwell or Nwell, if required are also inside these openings. This FOX is used to isolates the devices from one another or say active areas.

Surrounding the active layers with either the n-select or the p-select layers dopes the semiconductor n-type or p-type. Below diagram helps to understand the different combinations of active, p-select, n-select and N-well layers. You can think or visualize the different layers and their cross-sectional layer in the following way. Always remember – opening in the FOX is implanted by p-type / n-type if that location is determined by p-select mask / n-select mask.

You may be thinking that why n-select or p-select mask is greater than the Active mask/layer. Actually it depends on the alignment of the 2 masks. If p-select / n-select mask is properly aligned with the active layer mask then there is no need of any extra p-select around the Active layer. But to take precaution or avoiding any misalignment (which can stop to dope the active region with proper doping, either n type of p type), we keep the active layer mask smaller than the select layer mask.

Now let’s start comparing the different view of the CMOS inverter. Again – to understand the Side view, please go through the CMOS processing Series/Chapter.

Step 1: Draw N select, Nwell and P select layers.

Note: I haven’t draw the SiO2 layer here. Because this is our understanding that rest of the portion/area where no layer present, SiO2 is present.

Step 2: Draw Poly layer.

Note: This Poly in the layout is same for GATE Poly and FIELD POLY. In Few cases there are different layers are defined for these type of layers which helps CAD tool to recognize. In the lower technology (14nm, 10nm), sometime these two type of Poly layers also have different properties. Similarly, for PMOS and NMOS right now we are using same POLY layer but in lower technology (14nm, 10nm) these are also identify with different layer names. I will explain these things later on in some other article.

Step 3: Draw N+ Diffusion For NMOS. For PMOS Body Contact, Draw N-select, N+ diffusion.

Step 4: Draw P+ Diffusion for PMOS devices.

Step 5: Draw Metal Contact and Metal M1 which connect Contacts.

I think, now you can see that it’s far easy to draw a layout in comparison to the 3D view or Side view. But it’s far easy to understand in the 3D view and side view.

More familiar layout of CMOS inverter is below.

Note: We haven’t applied any design rules here or any type of layout design constraints. I just want to show you the differences in different view. We will discuss the design rules and layout design on the basis of design rules in next few articles in more detail.